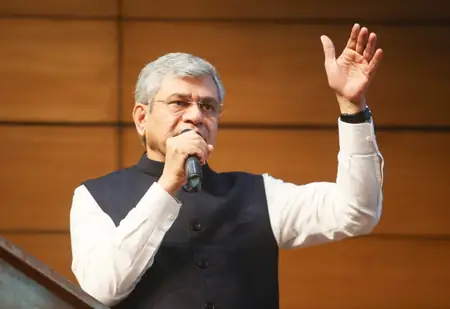

In a testament to India’s rising tech prowess, Minister Ashwini Vaishnaw revealed that the country is fast-tracking its goal of 85,000 semiconductor design engineers via the C2S program. This ISM flagship is transforming academic landscapes into innovation hubs.

Talent development takes center stage as the government invests heavily in skilling for the burgeoning chip sector. Early milestones in the 10-year program’s first phase underscore its effectiveness.

315 institutions now harness EDA tools from top-tier firms like Synopsys, Cadence, Siemens, Renesas, Ansys, and AMD. These resources empower students with practical chip design skills, vital for industry competitiveness.

From concept to completion, the SCL Mohali fabricates and validates student chips, offering a full-spectrum learning experience in design, fab, packaging, and testing.

Elevated to the world’s largest open-access EDA effort, the initiative has clocked 18.5 million+ hours of usage. Students nationwide—from diverse regions like J&K to Tamil Nadu—are actively contributing to semiconductor design.

Looking ahead, Vaishnaw forecasted the industry’s growth to $2 trillion, fueling demand for 2 million experts. This aligns perfectly with India’s youthful workforce, promising unprecedented job creation.

ISM 2.0 brings expansion to 500 institutions, amplifying talent development across the semiconductor value chain. India’s journey from chip importer to design leader is accelerating, driven by visionary policies and global partnerships.